- 您现在的位置:买卖IC网 > Sheet目录1995 > DS4625P+150/200 (Maxim Integrated Products)IC OSC CLOCK 200MHZ 10-LCCC

DS4625

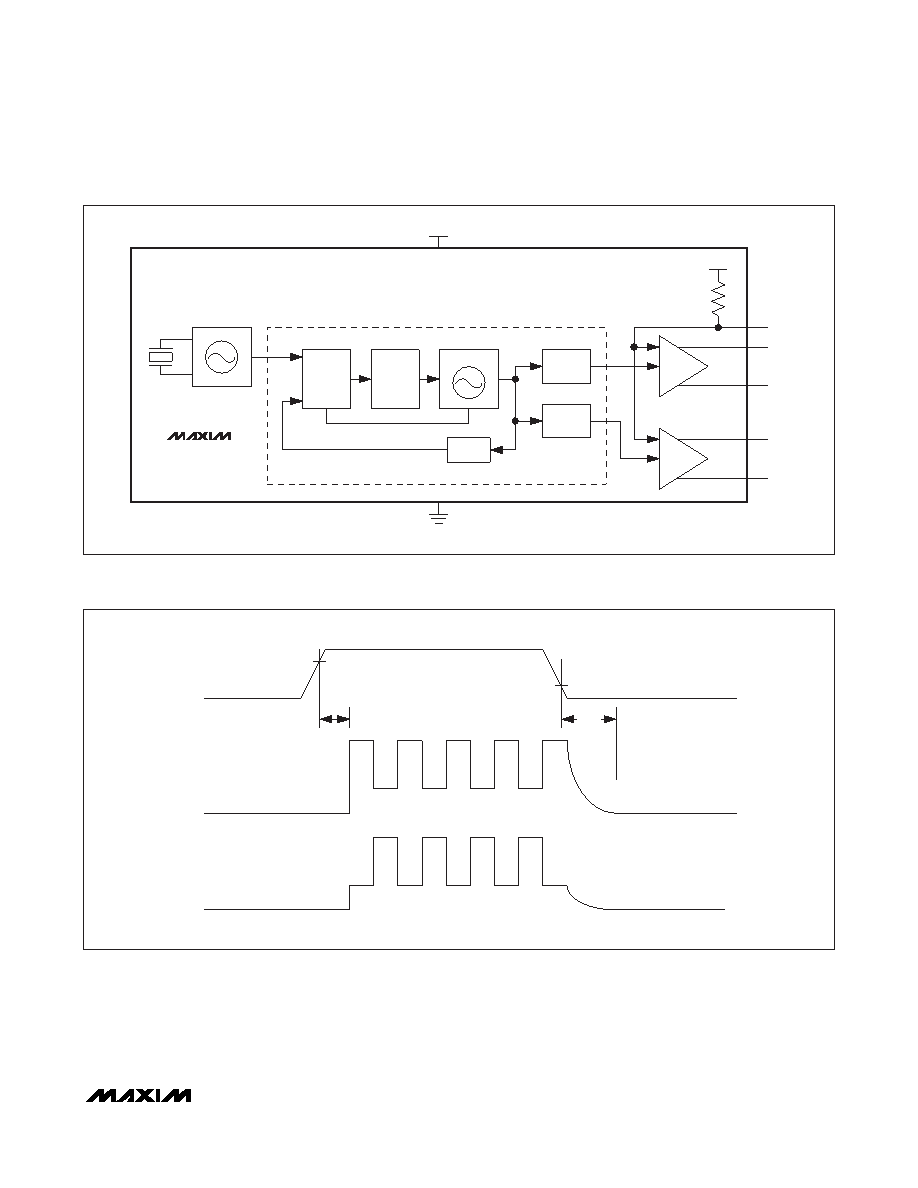

3.3V Dual-Output LVPECL Clock Oscillator

_______________________________________________________________________________________

5

X1

X0

PLL

X2

PFD

LPF

LC-VCO

DIV M

DIV P

DIV N

LVPECL

VCC

GND

OE

OP1

ON1

LVPECL

OP2

ON2

DS4625

RPU

VCC

Figure 1. Block Diagram

OE

OP_

tPZA

0.7 x VCC

0.3 x VCC

PECL_BIAS

ON_

tPAZ

Figure 2. LVPECL Output Timing Diagram When OE is Enabled and Disabled

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

DS4M133D+33

IC OSC CLOCK 133.33MHZ 10-LCCC

DS8005-RRX+

SMART CARD AFE DUAL 28SOIC

DSD1792DB

IC 24BIT STEREO AUD DAC 28-SSOP

EL5001IRE-T7

IC CLOCK DRIVER 6-CHAN 20-HTSSOP

FT10001L6X

IC RESET TIMER 6-MICROPAK

FT3001MPX

IC RESET TIMER 8-MLP

FT7521L6X

IC RESET TIMER 7.5SEC 6MICROPAK

FT7522L6X

IC RESET TIMER 6-MICROPAK

相关代理商/技术参数

DS4625P+156

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:3.3V Dual-Output LVPECL Clock Oscillator

DS4625P+200

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:3.3V Dual-Output LVPECL Clock Oscillator

DS463-K

制造商:Miyama Electric 功能描述:

DS463-R

制造商:Miyama Electric 功能描述:

DS463-W

制造商:Miyama Electric 功能描述:

DS464

制造商:Miyama Electric 功能描述:

DS465

制造商:Miyama Electric 功能描述:

DS468GKD

制造商:Schneider Electric 功能描述:SERVICE GROUND KIT FOR 600A DT SW